Cheaper to keep 'er Pg 54

EDN.comment Pg 10

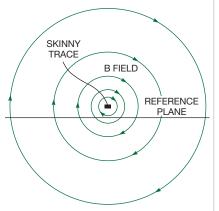

Signal Integrity: Field cancellation Pg 16

New devices for nanoelectronics Pg 18

Design Ideas Pg 45

Supply Chain Pg 51

### VOICE OF THE ENGINEER

### COMING SOON ...

### TO POWER STAGES EVERYWHERE

Issue 5/201

www.edn.com

# GaNpowIR®

POWERFUL COMPACT PERFORMANCE DAZZLINGLY EFFICIENCY STELLAR VALUE

International CRR Rectifier E POWER MANAGEMENT LEADER

Find out what's new!

digikey.com/new

Advertisement -

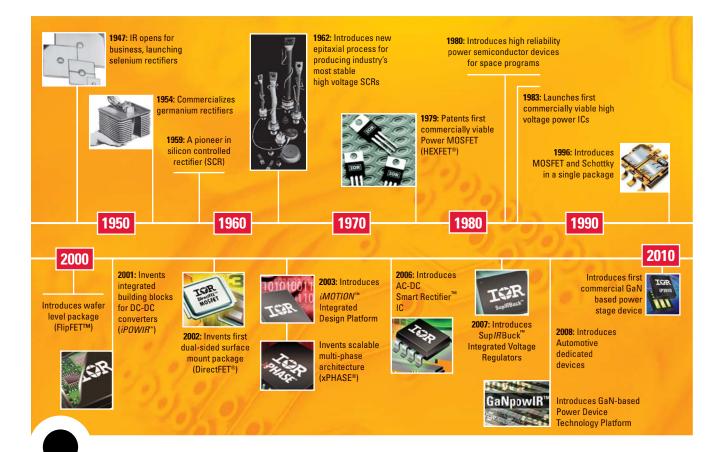

### AN EXCITING TIME

### BY MICHAEL A. BRIERE

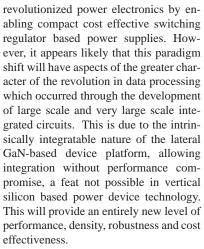

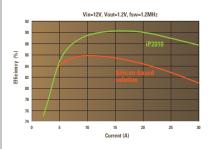

his is an exciting time in power electronics. Everything is about to change. The introduction of commercially viable GaN-based power devices in the 20 to 600 V application range will provide truly revolutionary performance/cost value to a variety of systems from lighting to motor drives and Class Daudio to ac-dc and dc-dc power supplies. This opportunity has been a long time in the making.

Ever since the discovery of the spontaneous formation of a two dimensional electron gas (2DEG) in the highly polarized AlGaN-GaN material system heterointerface by M. Asif Khan in 1991, the potential for superior power devices has been clear. The intrinsic advantages of this material system based HEMTs of high electron mobility and saturation velocity ( > 1600 cm<sup>2</sup>/Vs, > 2.5  $10^7$  cm/s respectively), high carrier density (10<sup>13</sup> cm<sup>-2</sup>), together with the high electric field stand off capability of the AlGaN and GaN materials ( > 1 MV/cm), provide the possibility of power switches with 10 to > 100times lower on-resistance than compaultimate performance possible within the multilayered hetero-epitaxial AlInGaN material system, or to provide devices for small niche applications, rather it has been on optimizing the performance to cost ratio within a manufacturable and reliable device technology platform.

The first issue to resolve involved the choice of substrate. A cursory review of the alternatives will show that only silicon substrates provide the necessary combination of cost, size, quality and volume of supply needed to support the broad power electronics market ( currently > \$ 10 B annual semiconductor content using > 10 Million six inch wafer equivalents

per year). The technological challenge of growing uniform high quality AlInGaN epitaxial layers on silicon substrates, made especially complex due to significant mismatches in both the lattice constants and their thermal coefficient of expansion, has to be met. The requisite control

GaNpowIR®

rable silicon based devices. In addition, the low parasitic capacitances of these intrinsically lateral devices allow for much lower switching times, an advantage leveraged in the fabrication of RF switches, as well as more efficient power devices.

The GaN-based power device program at International Rectifier, referred to as GaNpowIR<sup>®</sup>, has involved a long, costly and intense effort to turn, what has been to a large extent, an intellectual curiosity into a practical, commercially viable technology platform broadly applicable to the power electronic community. The focus has not been on achieving the of film thickness and compositional uniformities, epitaxial defects and macroscopic wafer warpage has been achieved on 150 mm silicon wafers through significant engineering efforts.

Next, the device design and fabrication process required additional significant attention. Here the first principle applied is that the fabrication process must be compatible with large volume silicon wafer manufacturing lines. This allows for the use of modern, highly capable equipment, as well as an overhead cost infrastructure competitive with the incumbent silicon based devices, a

pre-requisite for widespread adoption. This requirement, often abbreviated as "CMOS compatibility", requires that such III-V device stalwarts such as gold metallurgy, e-beam lithography and liftoff processes be abandoned. In addition, complex and highly costly processes involving re-growth of AlInGaN epitaxial layers for channel, drift or contact formation are likewise avoided. Standard inprocess and post process control methodologies must be applied to establish a high volume production platform. The device design and construction must not compromise on performance, quality or reliability metrics established by the incumbent silicon based technologies. This requires that off-state leakage be kept below 1 µA/mm gate length, significantly less than the 1 mA/mm often employed in the GaN-based device field to date. Similarly, on to off state current ratios must be greater than one million to be comparable to state-of-the-art silicon based power devices. This requires the use of low leakage epitaxial layers, as well as insulated gates, replacing the much more common Schottky metal-semiconductor structures.

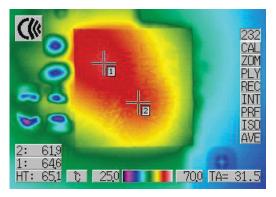

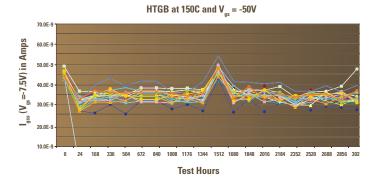

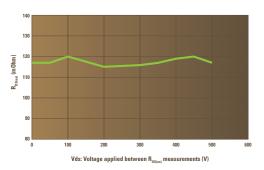

Device ruggedness in application conditions must also remain un-compromised with respect to expectations established by the incumbent silicon based technology. Large forward biased safe operating area is an important indication of such robustness. Device stability under accelerated stress conditions for extended periods of time is essential for acceptance in the power electronic community. To date, over 10,000,000 device hours of reliability data has been collected on the low voltage devices released to production by IR in early 2010, with up to 10,000 hours per device. No premature device failures have been found to date and parametric stability has been excellent. An example is shown in Figure 1, where the gate dielectric is stressed at -50 V, well above its device rating of -8.5 V for over 3.000 hours at 150°C without deleterious effect. It is imperative that such catastrophic failure mechanisms such as the "inverse piezo-electric effect", found

Continued inside of back wrap

Μ

TO A

Page 30

Cheaper to keep 'er Pg 54

EDN.comment Pg 10

Issue 5/2011

www.edn.com

Signal Integrity: Field cancellation Pg 16

New devices for nanoelectronics Pg 18

Design Ideas Pg 45

Supply Chain Pg 51

### VOICE OF THE ENGINEER

### BUILD ACCURATE SPICE MODELS FOR LOW-NOISE, LOW-POWER PRECISION AMPLIFIERS Page 20

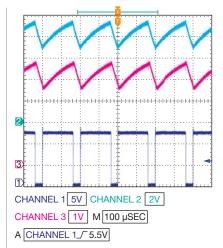

MONITOR PWM LOAD CURRENT WITH A HIGH-SIDE CURRENT-SENSE AMPLIFIER Page 39

> Find out what's new!

digikey.com/new

### Data acquisition just got a lot easier.

### More ways to control. More ways to connect.

The new Agilent 34972A Data Acquisition Switch Unit takes our best-selling Agilent 34970A to the next level. For starters, you get convenient built-in LAN and USB connectivity. Plus, you can control your data acquisition remotely via Web interface. And transfer logged data to your PC with a simple flash drive. No more expensive adapters and connectors. That's easy. That's Agilent.

| NEW 34972A                                                                    | 34970A                                             |  |  |  |  |

|-------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| USB and LAN                                                                   | GPIB and RS232                                     |  |  |  |  |

| Graphical web interface<br>Benchlink data logger software<br>SCPI programming | Benchlink data logger software<br>SCPI programming |  |  |  |  |

| 3-slot LXI unit with built-in 6 ½ digit DMM                                   |                                                    |  |  |  |  |

| \$1,845                                                                       | \$1,597*                                           |  |  |  |  |

© 2010 Agilent Technologies, Inc. \*Prices are in USD and are subject to change.

Agilent and our Distributor Network Right Instrument. Right Expertise. Delivered Right Now.

Buy from an Authorized Distributor www.agilent.com/find/distributors Learn how to connect wirelessly and get more FREE measurement tips at www.agilent.com/find/Agilent34972A

### Over 515,000 Products in Stock More Than 45,000 NEW Products Added in the Last 90 Days 440+ Suppliers

The industry's broadest product selection available for immediate delivery

### www.digikey.com 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

### MachX02. DO-IT-ALL DEVICES DEMAND A DO-IT-ALL PLD.

With the MachXO2 PLD family, you now have everything you need to meet your low power, small form factor, high functionality and low price requirements for your next consumer or system design.

Access free reference designs and software, development kits and supporting literature at: latticesemi.com/machxo2

### Applications

- Smart Phone

- Digital Camera

- GPS

- Server

- Router

- Base Station

And more ...

### **Benefits**

- Instant-on, non-volatile

- Flexible logic from 256 LUTs to 7,000 LUTs

- Embedded memory up to 240 Kbits

- Ultra low power as low as 19µW

- On-chip user flash memory & I<sup>2</sup>C, SPI, timer/counter

- Prices starting as low as \$0.75

And more ...

latticesemi.com/machxo2

©2010 Lattice Semiconductor Corporation. All rights reserved. Lattice Semiconductor Corporation, L (& design), Lattice (& design), MachXO2 and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries, in the United States and/or other countries. Other marks are used for identification purposes only, and may be trademarks of other parties.

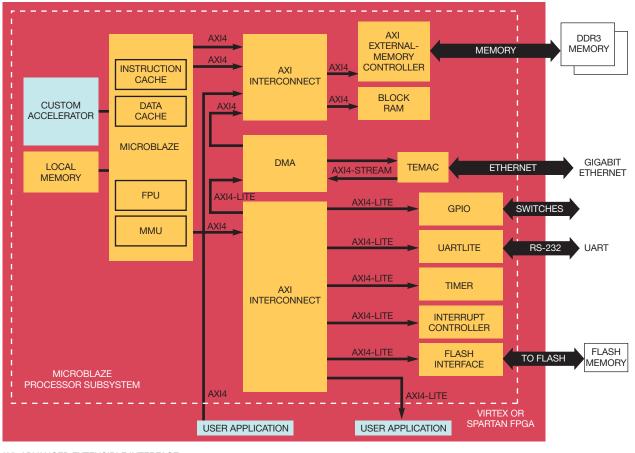

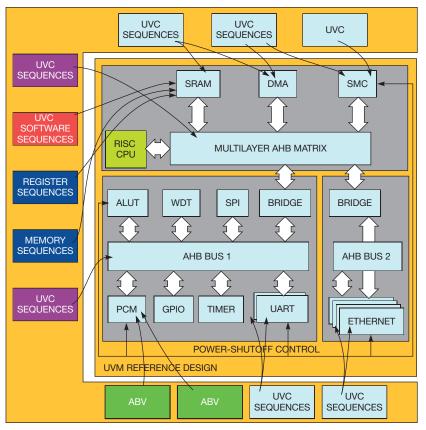

### CPUs in FPGAs: many faces to a trend

30 Whether as synthesizable soft cores or hard cores on the die, CPUs are showing up in more FPGA designs, bringing with them important challenges for designers.

by Ron Wilson, Editorial Director

## EDN 3.3.11 contents

### Build accurate Spice models for low-noise, low-power precision amplifiers

20 Understand Spice-model constructions to appreciate ac and dc performance. by Don LaFontaine, Intersil

### Dilbert 13

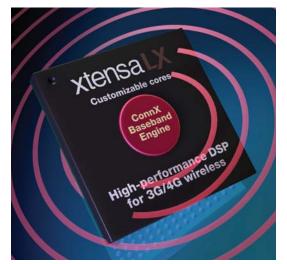

- 12 High-performance DSP-IP cores are ready for LTE-Advanced

- 13 Generator produces pulses to 330 MHz; functions, noise to 500 MHz

- 13 Analog, NI team up on simulation tool

- 14 Lighting platform brings building-block approach to LED lighting

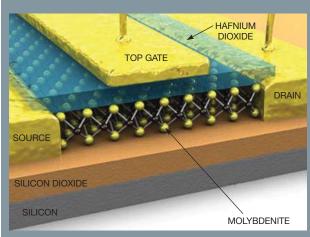

- 14 Molybdenite provides advantages over silicon, graphene

- 15 Processor touts 3G HSDPA, Android

- 15 Micrel introduces POL buck regulators

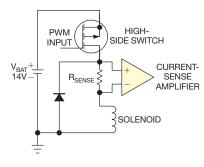

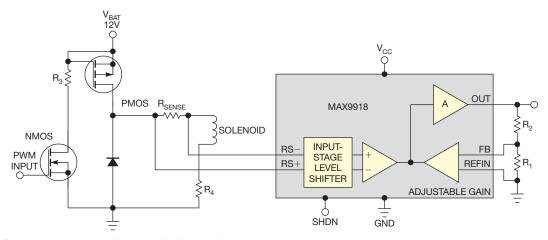

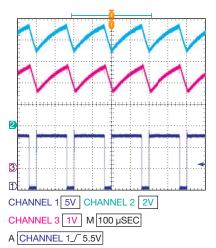

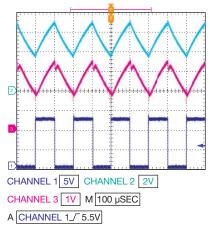

### Monitor PWM load current with a high-side current-sense amplifier

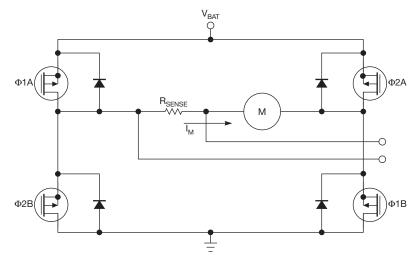

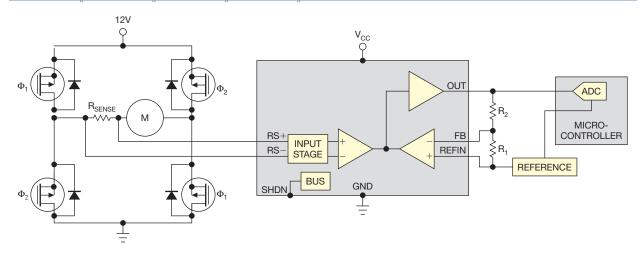

39 An innovative circuit allows you to monitor diodes' recirculating and power-supply current. by Maurizio Gavardoni and Akshay Bhat, Maxim Integrated Products

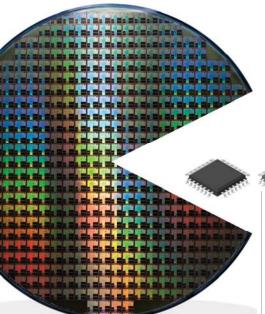

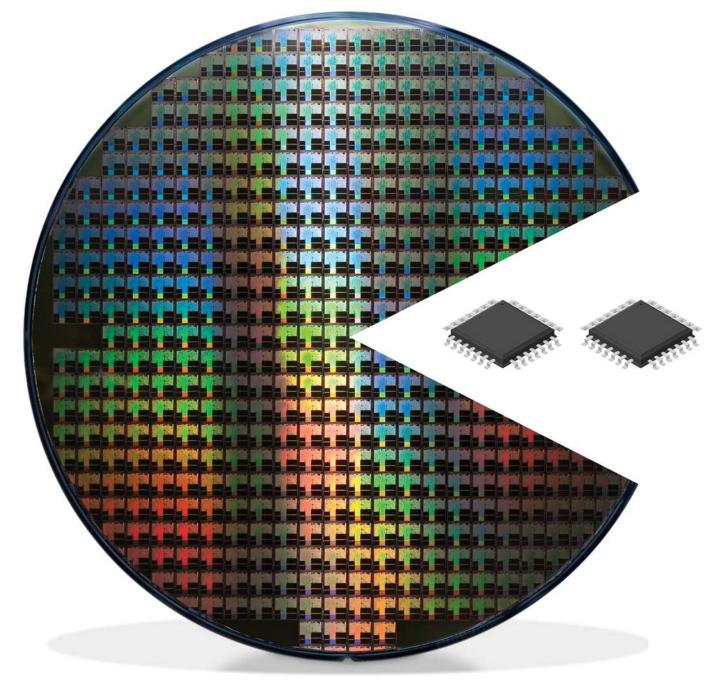

COVER: PHOTO-ILLUSTRATION BY TIM BURNS. WAFER: PHOTOMICK/ISTOCKPHOTO.COM; CHIPS: GRIMGRAM/ISTOCKPHOTO.COM

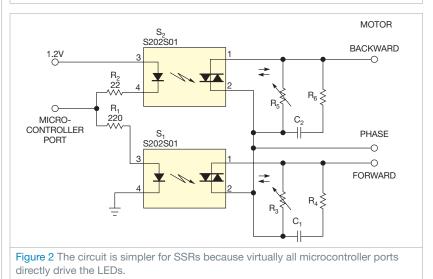

### DESIGNIDEAS

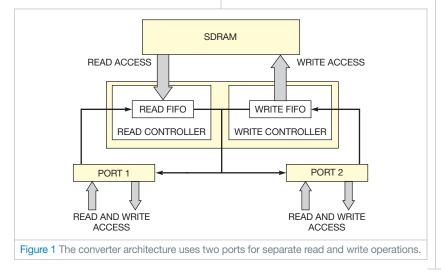

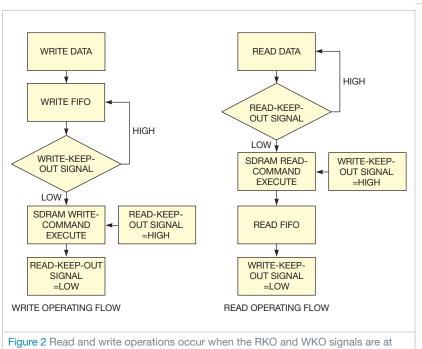

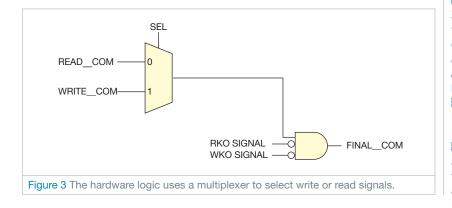

- 45 Design provides single-port-to-dual-port SDRAM converter

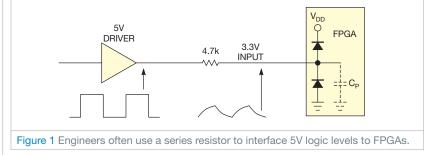

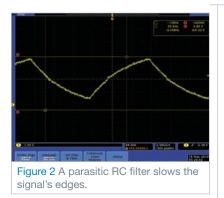

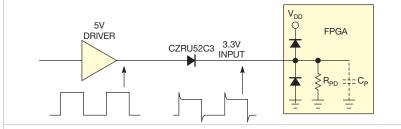

- 46 Zener diode protects FPGA inputs

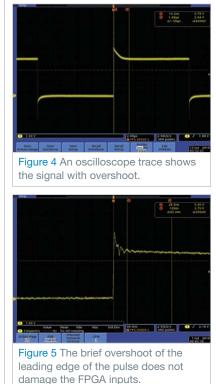

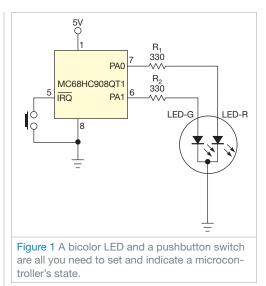

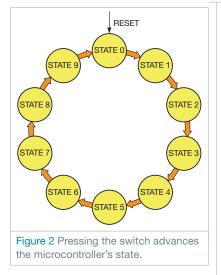

- 48 Bicolor LED indicates 10 states

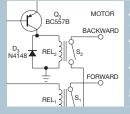

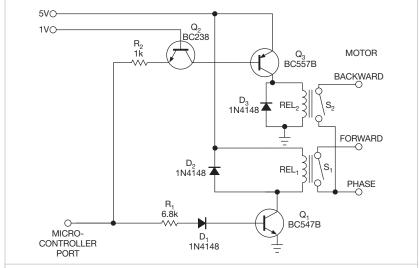

- 50 Relay driver switches two relays with one pin

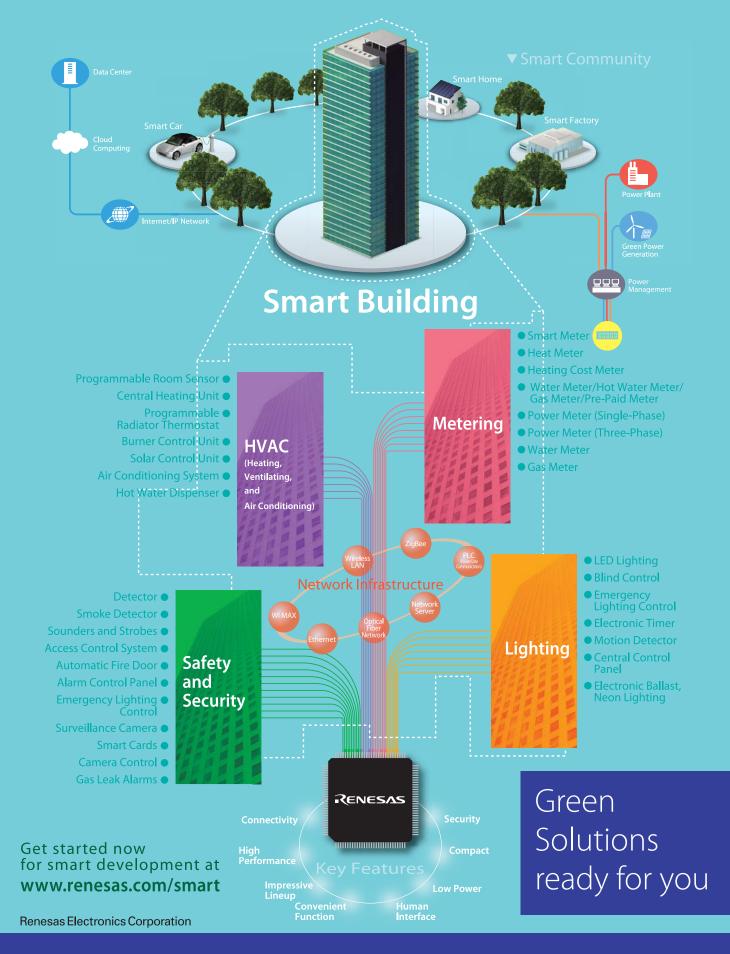

RENESAS

### contents 3.3.11

### **DEPARTMENTS & COLUMNS**

10 EDN.comment: Windows on ARM: for Intel, probably no cause for alarm

- 16 Signal Integrity: Field cancellation

- 18 Inside Nanotechnology: New devices for nanoelectronics

- 51 **Supply Chain:** Counterfeiting continues to grow, but the industry fights back

- 52 Product Roundup: Power Sources

- 54 Tales from the Cube: Cheaper to keep 'er

### **EDN** online contents

www.edn.com

### ONLINE ONLY

Check out this Web-exclusive article:

#### Fully depleted SOI shows its stuff in CPU design

An ARM Cortex M0 paper design suggests that FDSOI (fully depleted silicon on chip) could be a strong contender at 20 nm. →www.edn.com/110303toca

### JOIN THE CONVERSATION

Have you joined *EDN*'s Electronics Design Network on LinkedIn? If not, you're missing out on some great conversation. Here's what one group member has to say about *EDN*'s LinkedIn community: "It's really nice to see smart people who are passionate about their work go at it. You guys are an inspiration. You make *EDN* one of the better groups for engineers on LinkedIn."

Join the more than 2700 engineers and executives exchanging ideas in our group. →www.edn.com/110303tocb

# INNO ATION

Tune in to www.edn. com/innovation21 to see a list of the innovative engineers and products our editors selected as finalists in the 21st annual EDN Innovation Awards and then use the online ballot to cast your vote for the winners in each category. Don't delay! Voting ends March 31. www.edn.com/ innovation21

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 310/445-4200; FAX 310/445-4299. Periodicals postage paid at Los Angeles, CA, and at additional mailing offices. SUBSCRIPTIONS— Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. E-mail: EDN®kmpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Pymouth, MN 55447. Please provide old malling label as well as new address. Allow two months for change. NOTCE—Every precaution is taken to ensure accuracy of content; however, the publisher cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Pymouth, MN 55447. Canada Post: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to Pitney Bowes Inc, PO Box 25542, London, ON NGC 6E92. Copyright 2011 by United Business Media. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 56, Number 56 (Printed in USA).

### Simpler Power Conversion

IR's SmartRectifier<sup>™</sup> chipset for AC-DC power converters dramatically simplifies design and improves efficiency.

# TOTAL STREET

SmartRectifier<sup>™</sup> ICs Š

| Part<br>Number                 | IR1166<br>SPBF     | IR1167A<br>SPbF | IR1167B<br>SPbF | IR1168<br>SPbF | IR11662<br>SPbF    | IR11672A<br>SPbF | IR11682<br>SPbF |

|--------------------------------|--------------------|-----------------|-----------------|----------------|--------------------|------------------|-----------------|

| Package                        | S0-8               |                 |                 |                |                    |                  |                 |

| V <sub>cc</sub> (V)            | 20                 |                 |                 |                |                    |                  |                 |

| V <sub>FET</sub> (V)           | 200                |                 |                 |                |                    |                  |                 |

| Sw Freq.<br>max (kHz)          | 500 400            |                 |                 |                |                    |                  |                 |

| Gate Drive<br>±(A)             | +1/-4              | +2/-7           |                 | +1/-4          | +1/-4              | +2/-7            | +1/-4           |

| V <sub>gate</sub><br>Clamp (V) | 10.7               | 10.7            | 14.5            | 10.7           | 10.7               | 10.7             | 10.7            |

| Min. On<br>Time (ns)           | Program. 250 -3000 |                 |                 | 750            | Program. 250 -3000 |                  | 850             |

| Enable Pin                     | Yes                | Yes             | Yes             | No             | Yes                | Yes              | No              |

| Channel                        | 1                  |                 |                 | 2              | 1                  |                  | 2               |

| Automatic<br>MOT<br>Protection | No                 | No              | No              | No             | Yes                | Yes              | Yes             |

For more information call 1.800.981.8699 or visit www.irf.com

THE POWER MANAGEMENT LEADER

Visit us at Booth 409

Fort Worth Convention Center

🗖 07-09 March 2011

### BY BRIAN DIPERT, SENIOR TECHNICAL EDITOR

### Windows on ARM: for Intel, probably no cause for alarm

uring Microsoft's January International CES (Consumer Electronics Show) keynote address, Steve Ballmer, the company's chief executive officer, and Michael Angiulo, corporate vice president of its planning, hardware, and PC-ecosystem team, announced that the next-generation Windows OS would run on both x86 and ARM CPU architectures. In a sense, this announcement was no surprise. I disagree, however, with the pundits who reacted to the announcement by proclaiming that Intel—and AMD, and don't forget Via—were now dead. Many of these "experts" inaccurately drew parallels between Microsoft's announcement and Apple's several-year-old transition from PowerPC to x86 for OS X and subsequently to ARM for the OS X-derived iOS. In both Apple case studies, a wholesale migration from one CPU architecture to another took place, whereas the Microsoft case involves an expansion from one architecture to two.

Why does this distinction matter? Consider consumer desktop and mobile systems, which account for most of the x86 sales volume each year. The fundamental hardware costs of ARMand x86-based systems are comparable if not identical to each other. Assuming that cellular/broadband carrier or other service-provider subsidies don't factor into the equation, prices for the two CPUs' respective systems will be similar, as well.

As a consumer, why on earth would I choose an ARM-based variant with limited native-software support versus an x86-based alternative that continues to tap into an extensive backwardcompatible code ecosystem? And, if I were a developer, why would I bother compiling and supporting an ARM-flavored version of my app or, for that matter, a "universal" variant for the limited ARM customer base? ARM's situation shows little likelihood of success in today's consumer—or enterprise—desktop- and mobile-client scenarios. Microsoft went to great pains to point out that the code running on ARM-based hardware during the CES keynote demos was binary-compiled, not virtualized. But Ballmer and Angiulo also went to great pains to reiterate that AMD and Intel will continue as strong partners of Microsoft. Microsoft could provide dynamic binary-translation capabilities in Windows 8 for running x86 binaries on ARM hardware.

Such work-arounds are inherently imperfect, however, so why is Microsoft bothering with the ARM port at all? Servers, which are sensitive to power consumption and relatively insensitive to performance, are a possible reason. The required code support is less in this case than in the consumer market, and current draw and heat dissipation are ongoing concerns. But the enterprise is a conservative and slow-moving application area.

Looking at the suppliers' road maps, you might wonder why Microsoft is bothering to break away from its x86-exclusive embrace. I've long said that Intel won't be able to seriously compete with ARM on ARM's own turf until at least the third turn of the Atom tick-tock cadence. That prediction is coming to pass right on schedule. First-generation Atom on a 45-nm process essentially created the low-cost notebook-that is, the netbook. Second-generation Atom, also on a 45-nm process, has established a beachhead in tablets. Intel's now-mature 32-nm process is the basis for the upcoming third-generation Atom silicon spin. The next-generation 22-nm process will also inevitably yield highly integrated and power-sensitive Atom-based products. Meanwhile, AMD is translating its Fusion aspirations into product reality, and Via has migrated its dual-core Nano CPU into 40-nm-based monolithic-die form. By the time Windows 8 appears, the low-power x86 story should be in solid shape.

Perhaps, then, the more accurate question to ask is, Why is Microsoft breaking away from its ARM-exclusive embrace? With a nod to Tony King-Smith, vice president of marketing at Imagination Technologies, who gave me this idea, I believe a code-base simplification move is under way: the eventual obsolescence of Windows CE in favor of a unilateral corporate focus on modularized Windows 8 across all product segments in which Microsoft plays.

So, consider this potential future scenario: Microsoft broadens Windows 8 beyond x86 to ARM to catch the eye of mobile-electronics-equipment developers that might otherwise standardize on some other operating system and application suite. By the time Microsoft releases Windows 8, x86 CPU suppliers will be ready with silicon that's good enough from performance and power-consumption standpoints versus ARM alternatives. And developers go with x86 instead of the ARM processors they'd previously used. Wouldn't that be ironic?EDN

+ Read an expanded version of this column on the Brian's Brain blog at www.edn.com/110303eda.

### EDN

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-925-736-7617; judy.hayes@ubm.com

EDITORIAL DIRECTOR Ron Wilson 1-415-947-6317; ron.wilson@ubm.com

MANAGING EDITOR Amy Norcross Contributed technical articles 1-781-869-7971; amy.norcross@ubm.com

### MANAGING EDITOR-NEWS

Suzanne Deffree Electronic Business, Distribution 1-631-266-3433; suzanne.deffree@ubm.com

SENIOR TECHNICAL EDITOR Brian Dipert Consumer Electronics, Multimedia, PCs, Mass Storage 1-916-548-1225; brian.dipert@ubm.com

TECHNICAL EDITOR Margery Conner Power Sources, Components, Green Engineering 1-805-461-8242; margery.conner@ubm.com

#### TECHNICAL EDITOR Mike Demler EDA, IC Design and Application 1-408-384-8336; mike.demler@ubm.com

TECHNICAL EDITOR Paul Rako Analog, RF, PCB Design 1-408-745-1994; paul.rako@ubm.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@ubm.com

SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-869-7969; frances.granville@ubm.com

ASSOCIATE EDITOR Jessica MacNeil, 1-781-869-7983; jessica.macneil@ubm.com

CONSULTING EDITOR

Staff Scientist, Linear Technology edn.editor@ubm.com

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com Robert Cravotta robert.cravotta@embeddedinsights.com COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

> LEAD ART DIRECTOR Marco Aguilera

ASSOCIATE ART DIRECTOR Tim Burns

> PRODUCTION Jeff Tade,

Production Director Brian Wu, Publications Production Manager Jeff Polman, Derric Treece, Senior Production Artists William Baughman, Lucia Corona, Ricardo Esparza, Production Artists

**EDN EUROPE** Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.fr

EDN ASIA Wai-Chun Chen, Group Publisher, Asia waichun.chen@ubm.com Kirtimaya Varma, Editor-in-Chief kirti.varma@ubm.com

EDN CHINA William Zhang, Publisher and Editorial Director william.zhang@ubm.com Jeff Lu, Executive Editor jeff.lu@ubm.com

EDN JAPAN Katsuya Watanabe, Publisher katsuya.watanabe@ubm.com Ken Amemoto,

Editor-in-Chief ken.amemoto@ubm.com

Paul Miller, Chief Executive Officer David Blaza, Vice President, UBM Electronics

Karen Field, Senior Vice President, Content Fred Gysi,

Chief Financial Officer Mike Deering, Chief Technology Officer Stephen Corrick, Vice President/Executive Director

Kevin O'Keefe, Senior Vice President, Events Division

Roger Burg, Vice President, Operations Jason Brown, Vice President, E-media

UBM Electropics EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change.

UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

### **MAXIMUM RELIABILITY** In contact, stability and low-noise performance

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance

- through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

SLC Connector Assemblies

### Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

MILL-MAX

www.mill-max.com/EDN596

# INNOVATIONS & INNOVATIONS

### High-performance DSP-IP cores are ready for LTE-Advanced

ensilica's new ConnX BBE64-128 DSP-IP (intellectual-property) cores for SOC (system-on-chip) design extend the BBE (baseband-engine) family to more than 100 billion MAC (multiply/accumulate)operations-per-sec performance to meet requirements for the emerging LTE (long-term evolution)-Advanced standard. Tensilica manufactures the ConnX BBE64-128 DSP core for LTE-Advanced in a high-performance, 28-nm process technology to deliver more than five times the required computing power of LTE. The LTE-Advanced specification requires an increase in peak data rate from 150 Mbps to 1 Gbps, with an increase in channel bandwidth from 20 MHz to 100 MHz.

Tensilica based the BBE64-128 on a multislot VLIW (very-long-instruction-word) architecture that enables 128 MAC operations per cycle for maximum throughput and minimum energy consumption. It also performs common MIMO (multiple-in/multiple-out) functions, FIR (finite-impulse-response) filtering, and channelestimation functions for LTE-Advanced. Modeless switch to Tensilica's smaller standard 16and 24-bit instructions enables high code density for nonvector algorithms. The BBE64-128 also includes a single-cycle, 16-way complex radix-4 and radix-8 FFT (fast Fourier transform) and DFT (discrete Fourier transform) for efficiency on arbitrarily sized transformations in LTE OFDM (orthogonal-frequency-divisionmultiplexing) algorithms.

The company based the ConnX BBE64-UE for LTE-Advanced handset applications on a smaller feature set to minimize energy consumption and latency. It excludes some of the features of the BBE64-128, such as the option to run 128 MAC operations/cycle, to achieve

higher efficiency. The BBE64-UE processor can reach approximately 300,000 GMACs/ sec/W, and Tensilica manufactures the core in a low-leakage, 28-nm-process technology.

EDITED BY FRAN GRANVILLE

With Tensilica's automated tools, you can optimize your design for specific applications by adding custom instructions, and you can add special memory interfaces, special per-SIMD (single-instruction/multiple-data) lane look-ups, or other required functions. The customizable processor architecture allows you to tailor functions, turn them on or off, and add them during SOC design.

Tensilica's design process automatically generates the compiler for the BBE64 core to match the configuration options you choose and features full native DSP-data support, including integer, fractional, real, and complex. It automatically infers complex instructions, accelerates and vectorizes legacy code from ConnX BBE16, accelerates legacy code for

industry-standard intrinsic functions, vectorizes loops with complex conditional operations, and performs ANSI C operators on vector-data types. An "analysis cockpit" provides for program analysis, including a vectorization assistant.

A complete evaluation kit for the ConnX BBE64-128 and ConnX BBE-UE cores should become available for early-access customers in the fall.

—by Mike Demler ▶Tensilica, www.tensilica.com.

### **TALKBACK**

"I have a bigbrother version that I have had for over 20 years. I opened it once because of a strange smell. That poor mouse."

--Reader Dick Kolman, in EDN's Talkback section, at http://bit.ly/fh5HGW. Add your comments.

The Tensilica ConnX BBE64 DSP-IP cores support LTE-Advanced infrastructure and handset applications.

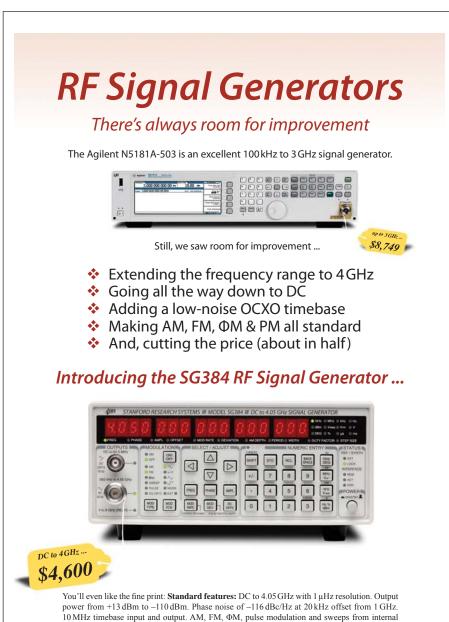

### Generator produces pulses to 330 MHz; functions, noise to 500 MHz

gilent Technologies has expanded its pulse/ function/arbitrary-noisewaveform generator family to help design and test

engineers improve the efficiency and precision of testing higherspeed, higher-bandwidth, analog-, digital-, and mixed-signal devices. Engineers must improve quality yet must get to market faster with products whose features differentiate them from those of competitors. These conflicting requirements necessi-

tate expanded test capabilities during development. The Agilent 81160A provides innovative functions and streamlined setup to help you more quickly complete expanded test protocols.

The generator eliminates the need for cumbersome multi-

The 14-bit-resolution, 2.5G-sample/sec-datarate 81160A extends the frequency range of the manufacturer's pulse/function/arbitrarynoise-waveform generator family to 330 MHz for pulses and 500 MHz for functions and noise.

> instrument setups for stresstesting devices. The 81160A provides versatile waveforms as well as signals with an intrinsic

jitter of 7 psec rms. The instrument targets use in general-purpose bench tests and advanced serial-data stress tests. It gener-

> ates 330-MHz pulses, optionally generates pulse patterns, and generates 500-MHz functions and arbitrarynoise waveforms with a 2.5G-sample/sec data rate and 14-bit vertical resolution. Selectable crest factors for white gaussian noise allow you to determine how much distortion to apply to a device during stress testing to meet various serial-bus

standards. Glitch-free timingparameter adjustments let you change the frequency without dropouts or glitches and enable

### Analog, NI team up on simulation tool

A nalog Devices Inc and National Instruments recently announced their collaboration on a new release of NI's Multisim component-evaluation tool with added features to provide engineers with an easy-to-use environment for the simulation of linear circuits using Analog Devices' components. The free component-evaluation tool is

available on Analog Devices' Web site.

This edition of the tool allows engineers to design larger, more complex circuits and easily import their own models into the tool. By matching more than 1000 of Analog Devices' amplifiers, switches, and voltage references to more than 550 of National Instruments' simulation models, designers have free access to the simulation environment, allowing them to easily experiment with circuit designs and reduce system-development time and cost.

"Finding the right solution for a linear circuit often means sorting through many products and specifications," says Steve Sockolov, director of the Precision Signal Conditioning

**DILBERT By Scott Adams** WE'RE LUCKY TO SOME MIGHT CALL MEET OUR NEW HIM UNQUALIFIED, HAVE HIM DESPITE VICE PRESIDENT HIS UTTER LACK OF BUT I CALL HIM OF ENGINEERING. EXPERIENCE IN OUR EXOTIC. INDUSTRY. YOU'RE OVER-SELLING.

continuous operation without rebooting or resetting the device under test. Arbitrary bit patterns allow simple pattern settings to emulate capacitive loading of the channels and eliminate the need for complex measurement setups to test designs to their limits. Noise waveforms' maximum duration-that is, the period during which patterns do not repeat-is 20 days, yet you can exactly and repeatedly reproduce brief portions of such waveforms to quickly investigate unusual behavior of the system under test.

The suggested US entry price for a single-channel version of the 81160A 330-MHz (pulse)/500-MHz (function/ arbitrary-noise) generator is \$16,900. A two-channel version costs \$20,000.

by Dan Strassberg

Agilent Technologies, www.agilent.com/ find/81160.

Group at Analog Devices. "We offer innovative ways to help customers quickly find what they need."

The NI Multisim Component Evaluator-Analog Devices Edition provides engineers the ability to build simulatable circuits to evaluate a library of Analog Devices' operational amplifiers, switches, and voltage references. It also provides Spice-parser improvements, updated BSIMs (Berkeley Short-Channel IGFET Models), support for advanced parameters and enhanced digitalsimulation accuracy, improved design communication with on-page connectors, and a new WYSIWYG net-naming system.

-by Paul Rako

► Analog Devices,

www.analog.com.

► National Instruments,

www.ni.com.

### pulse

### Lighting platform brings building-block approach to LED lighting

Some companies are chasing after the retrofit market of LEDs that fit into incandescent lighting systems, but Tyco Electronics instead targets the next generation of LED-lighting systems, designing them from the ground up to exploit the advantages of solid-state lighting. With its new Nevalo lighting system, Tyco is betting that a modular

approach will prove to be the winning one.

By concentrating on new lighting wins, the Nevalo system need not fit into current form factors of light bulbs, luminaires, or tubes and instead introduces a building-block approach to lighting design. The Nevalo platform includes light modules, drivers, optics, wiring systems, and software tools to evaluate thermal management and price and performance

budgeting.

The Nevalo system includes more than 60 LED-light modules ranging from 300 to 3400 lumens in form factors for common lighting applications; optics in total internal reflection and reflector styles; drivers with constant-current output, dimming-control capabilities, and temperature monitoring; and a new ribbon-based, four-wire wiring-configuration system keyed and color-coded for ease of manufacturing. The system includes circuit-protection devices and heat sinks that match the LED-light modules to help provide appropriate ther-

mal management and life expectancy.

The LED-light-module subsystem comprises a PCB (printed-circuit board), including LEDs, thermal-interface material, a socket for circular applications, and matching optics. By mixing and matching the components, designers can create down lights, sconces, and track-lighting equivalents. Prices for systemdevelopment kits range from \$249 to \$399.

−by Margery Conner ▶Nevalo, www.nevalo.com.

03,03,

(b)

The Nevalo lighting system

Tyco Electronics

for lighting applications such as track lights (a) offers modularized optics, LEDs, power management, and thermal units for solid-state lights (b).

### Molybdenite provides advantages over silicon, graphene

Researchers at Switzerland's EPFL (École Polytechnique Fédérale de Lausanne) are touting molybdenite, or  $MoS_2$ , for use in electronics (Reference 1). Using the material would enable manufacturers to develop smaller and more energy-efficient electronic chips. The mineral is abundant in nature, but no one

33.55

Manufacturers can use molybdenite to create an ultra-lowpower FET by acting as its channel on a silicon-on-insulator substrate. had previously studied it for use in electronics.

"It's a 2-D, very thin material and easy to use in nanotechnology," says Andras Kis, a professor at EPFL. "It has real potential in the fabrication of very small transistors, LEDs, and solar cells." Molybdenite is also less voluminous than silicon, a 3-D material. "In a 0.65-nmthick sheet of molybdenite, the electrons can move around as easily as in a 2-nm-thick sheet of silicon," Kis says. "But it's not currently possible to fabricate a sheet of silicon as thin as a monolayer sheet of molybdenite."

Researchers also claim that molybdenite can yield transistors that consume 100,000 times less energy in a standby state than traditional silicon transistors. Manufacturers must use a semiconductor with a gap to turn a transistor on and off, and molybdenite's 1.8-eV (electron-volt) gap is ideal for this purpose. This gap also gives it an advantage over graphene, which lacks this gap.—by Suzanne Deffree

École Polytechnique Fédérale de Lausanne, www.epfl.ch.

### REFERENCE

Radisavljevic, B, et al, "Single-layer MoS<sub>2</sub> transistors," *Nature Nanotechnology*, January 2011, http://bit. ly/ih8lrR.

### Processor touts 3G HSDPA, Android

Broadcom's new BCM-2157 HSDPA (highspeed-downlink-packetaccess) baseband processor integrates simultaneous 3G (third-generation) HSDPA connectivity at downstream media technology and video applications with resolution as fine as 432×320-pixel HVGA (half-size video-graphics array), a 5M-pixel camera, and the ability to encode and decode H.264 video at 30 frames/sec.

The BCM2157 integrates a baseband processor for 3G HSDPA cellular communications with an application processor for low-cost Android smartphones.

rates as fast as 7.2 Mbps with advanced smartphone features for mass-market mobile handsets. The BCM2157 modem also supports WCDMA (wideband-code-division-multipleaccess) and EDGE (enhanced

Support for mobile-hotspot functions enables handsets to share a 3G connection with eight devices.

data rates for global-systemfor-mobile-communicationsevolution) networks.

The dual-core device employs a dedicated, 500-MHz ARM11 processor to support multitouch, advanced multiBroadcom manufactures the BCM2157 in a low-power, 65-nm CMOS process. Support for mobile-hot-spot functions enables handsets to share a 3G connection with as many as eight simultaneous devices or users through Wi-Fi. Two SDIO (secure-digital-input/output) ports provide for connections to off-chip wireless-LAN transceivers and SD (securedigital) MMC (multimedia cards).

The device also provides a USB (Universal Serial Bus) 2.0 port, along with audio amplifiers for driving 100-mW headsets, dual digital microphones, and a built-in five-band audio equalizer. The audio DSP supports Broadcom's M-Stream technology with the GSM (globalsystem-for-mobile)-communications SAIC (single-antennainterference-canceling) standard. An on-chip PWM (pulsewidth modulator) drives a vibrator to notify users of received calls.

The BCM2157 modem supports 3G dual SIM (subscriberidentification-module)/dualstandby technology and AMR-WB (adaptive multirate wideband) for HD (high-definition) voice calls over 3G networks. Dual-SIM is not in the Android standard, but it is a growing requirement in parts of the world that lack number portability. With two SIM cards, subscribers can migrate between carriers and receive calls on different numbers.

The BCM2157 supports Android version 2.2 Froyo but not the Adobe Flash-player 10.1 feature of that version of Google's operating system, which requires more advanced processors. The device also integrates Broadcom's proprietary InConcert technology, which supports interoperability of devices in the 2.4-GHz frequency range, coordinat-

ing transmissions to optimize throughput in Bluetooth, Wi-Fi, GPS (global-positioning-system), and NFC (near-field-communications) applications. Digital-audio ports include I2S (interintegrated-circuit sound) and PCM (pulse-code modulation), with a UART (universal asynchronous receiver/transmitter) to interface to transceivers for Bluetooth earpieces or FMband radios. A BSC (Broadcom serial-control) bus connects to an off-chip PMU (power-management unit).

The BCM2157 platform employs technology from the earlier dual-core BCM2153 architecture, which targets Symbian (www.symbian.com) and Windows Mobile operating systems and finds use in Samsung's (www.samsung.com) bada handsets.

The device is now available for sampling to early-access customers, and the company plans its first commercial launch for this quarter.

- by Mike Demler ▷Broadcom, www.broadcom.com.

> 0 0

### MICREL INTRODUCES POL BUCK REGULATORS

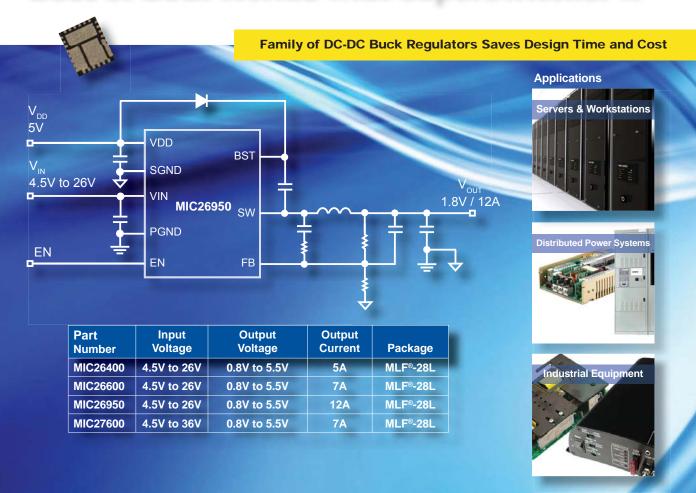

Micrel recently introduced the MIC26400, MIC26600, and MIC26950 POL (point-of-load) synchronous buck regulators, all of which feature digitally modified adaptive on-time-control architectures and operate over an input-supply range of 4.5 to 26V and an adjustable output voltage as low as 0.8V. The devices employ Micrel's Hyper Speed Control architecture, which allows for fast transient response, reduces output capacitance, and enables high-input-voltage and lowoutput-voltage operation. They also include undervoltage lockout to ensure proper operation under powersag conditions, internal soft-start to reduce inrush current, foldback-current limit, "hiccup"-mode short-circuit protection, and thermal shutdown. Typical accuracy is ±1%, and the devices operate at a switching frequency of 300 kHz. Prices for the MIC26400, MIC26600, and MIC26950 start at \$1.82, \$2.20, and \$2.77 (1000), respectively. - by Paul Rako Micrel, www.micrel.com.

SIGNAL INTEGRITY

### BY HOWARD JOHNSON, PhD

### Field cancellation

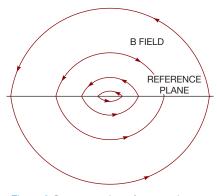

**igures 1**, **2**, and **3** illustrate the pattern of magnetic fields surrounding one microstrip trace on a typical PCB (printedcircuit board). The trace appears in cross-sectional view as a small black rectangle. The line below the trace represents a solid plane layer within the board, which may contain other signal layers not shown. Current on the trace flows into the

page in all three cases.

Figure 1 shows the pattern of magnetic lines of force resulting from the

Figure 1 One current by itself creates magnetic fields in simple concentric patterns.

current on the trace, without considering current on the reference plane. This pattern of lines looks like a nested set of concentric circles. As you move to a distance r away from the trace, the field intensity falls off as 1/r. An infinite straight wire suspended in free space generates this same familiar pattern.

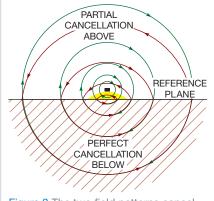

In a singled-ended system, outgoing current on the trace stimulates an equal and opposite current returning to its source through the power and ground system. **Figure 2** depicts the magnetic field resulting from that current. At frequencies higher than approximately 1 MHz on a typical PCB, current returning to its source flows along the top surface of the solid reference plane, parallel to the outbound trace. The current

Figure 2 Current on the reference plane creates its own pattern of magnetic fields.

Figure 3 The two field patterns cancel perfectly in the region below the plane.

bunches strongly right underneath the signal trace, with a distribution that falls off rapidly as you move away from the trace on either side. The pattern of magnetic fields from this distribution makes football-like shapes. Where each line of force intercepts the solid plane, it "bends" in proportion to the profile of current flowing in the sheet at that location. These lines of force circulate in a direction opposite those in **Figure 1**.

When you superimpose the two patterns, the fields in the bottom half of the diagram cancel perfectly, assuming a reference plane of infinite extent and perfect conductivity (Figure 3). The field intensity above the trace does not cancel perfectly, but it substantially cancels, vastly reducing both crosstalk and EMI (electromagnetic interference) on that side. The field intensity increases only in the small yellow region directly under the trace, at which point it approximately doubles. The net benefit is fantastic. There is no simpler or more effective means of combatting crosstalk and EMI than a solid reference plane.

I love the field-cancellation benefit, but who knew that fields do what they do so well? James Clerk Maxwell, in his seminal text, A Treatise on Electricity and Magnetism, published in 1891 by Clarendon Press, explains in volume two, article 654, that current flows in the solid reference plane in reaction to the current flowing in the trace. The reference-plane currents, called eddy currents, form in a pattern that neutralizes the component of the magnetic field normal to the reference plane. The solution in Figure 3 attains that goal, perfectly canceling the vertical component of the magnetic field at the surface of the solid reference plane. Were some portion of the field to behave differently, it would set up eddy currents in the plane that would counteract the miscreant field, forcing it back into the shape shown in Figure 3.EDN

Howard Johnson, PhD, frequently conducts technical workshops for digital engineers. Visit his Web site at www.sigcon.com.

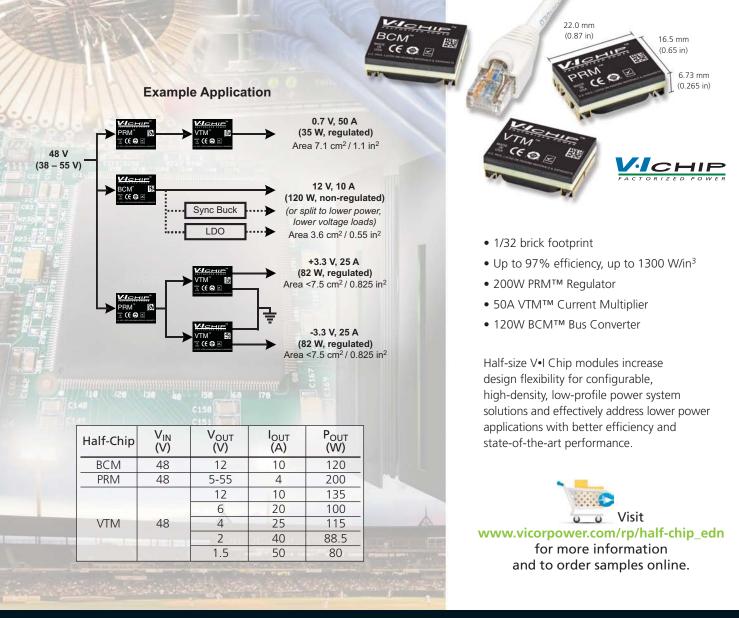

### Twice the Power Half the Size

New family of high-density power components enables fast, adaptable designs

### All parts available from stock NOW!

vicorpower.com/rp/half-chip\_edn

VICOR

BOOTH #108

INSIDE NANOTECHNOLOGY

### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

### New devices for nanoelectronics

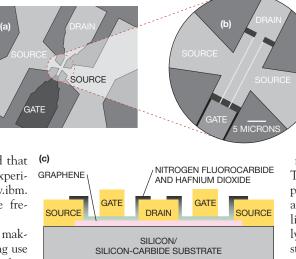

anoelectronics holds the promise of advanced capabilities for computing, RF and communications, and memories. One of the challenges in exploiting these capabilities is being able to manufacture, model, and test these devices. Manufacturers are creating these new devices not only in smaller versions of traditional devices, as in the standard semiconductor industry for CMOS, but also in new device construction and device materials.

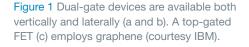

Many of these devices use graphene as a key material in gates, epitaxial layers, and interconnects. The challenge with using graphene as a switch or a transistor material is that it lacks the bandgap that normally occurs in CMOS processes. As a result, manufacturers have created new structures, such as doped "dual"-gate devices. These devices provide the high-performance transporting and conduction aspects of the graphene and still allow for use in common-architecture circuit de-

sign. Manufacturers construct the dual-gate devices both vertically with a top gate and a back gate beneath the graphene layer or laterally with adjacent gates. The manufacturers can fabricate these devices with modifications of standard CMOS processes (Figure 1). These devices

offer performance well beyond that of standard CMOS devices; experimental data from IBM (www.ibm. com) shows a typical device frequency as high as 170 GHz.

Carbon nanotubes are also making headway in circuits, finding use both in high-performance conductance channels as enhancements to standard CMOS and in interconnect. Vias and contacts use the nanotubes for interconnect to provide low-resistance, high-current pathways. Vendors form the contacts and vias using an alloy of titanium/lead/gold/ carbon nanotubes.

For communications, the high speed available in nanotechnology is driving advancement in optical interconnect and devices. Recent advances in zincoxide-silicon radial heterojunctions have produced nanorods and nanopillars that exhibit dramatic improvements over standard photodetectors. The increased vertical sur-

face area for the vertical nanorod demonstrates a high gain in photoconductivity due to the enhanced surface electron-hole separation. This gain leads to an approximately 2.5-times-higher responsivity to ultraviolet light over a planar structure of the same thickness.

On the memory side, a number of new technologies are in progress. These nanotechnology memories include PCM (phase-change memory), RRAM (resistive random-access memory), MTI (magnetic-tunnel junction), MRAM (magnetoresistive randomaccess memory), STT (spin-transfertorque), MQCA (magnetic-quantum cellular automa), and traditional flash devices. All of these nonvolatile memory technologies are working on retention and low-power read and write access with error-correction schemes. These characteristics, including the ability to read, program, and rewrite the state of cell at high density, are driving the new memory investigations. These technologies all focus on manipulation of magnetic or material properties of the storage cell. With nanomanufacturing, these cells are now small enough to manipulate and large enough to let you know whether programming has occurred.

> These technologies are trying to surpass the density and power of the NANDflash cell. The cell size for NAND flash, now down to 0.0028 square microns for a 25-nm process, is having scaling issues because the cell stores so few electrons as a delta between states. As a result, there will soon be no

measurable difference in the states. The scaling has progressed to the point at which, on a 25-nm process, a 5% variation in cell delta, due to line edge roughness, is approximately three silicon lattices. The current state of NAND-flash technology is 64-Gbit MLC (multilevel-cell) design.EDN

Pallab Chatterjee is on the IEEE Nanotechnology Council.

# Power Density AND Performance — Get the Best of Both Worlds with SuperSwitcher II<sup>™</sup>

In today's power-hungry applications, there is an insatiable need to deliver high levels of current while maximizing efficiency and minimizing board space. Micrel's SuperSwitcher II<sup>™</sup> high power density buck regulators are an ideal fit.

The SuperSwitcher II<sup>™</sup> integrated FET DC-DC buck regulators are optimized to deliver world class power density coupled with simplicity of use. Ultra-fast transient response, high efficiency, extremely low duty cycle operation and Any Capacitor<sup>™</sup> stable are all merged together to make the SuperSwitcher II<sup>™</sup> family easy to use with a reduced BOM cost.

For more information, contact your local Micrel sales representative or visit Micrel at: www.micrel.com/ ad/superswitcherll.

### **Key Features**

- Any Capacitor™ Stable No Stability Issues with Distributed Capacitance, ESR Changes

- High Delta V Operation Can Eliminate Intermediate Supplies and Improve System Efficiency (36V<sub>IN</sub>, 0.8V<sub>OUT</sub>)

- Fast Transient Response Allows for Smaller, Less Expensive Output Capacitors

- Constant Frequency Operation Simplifies EMI Design

© 2011 Micrel, Inc. All rights reserved. Micrel and Innovation Through Technology are registered trademarks of Micrel, Inc. SuperSwitcher II and Any Capacitor are trademarks of Micrel, Inc. MLF is a registered trademark of Amkor Technology.

www.micrel.com

### BUILD ACCURATE SPICE SPICE MODELS FOR FOR LOW-NOISE, LOW-POWER PRECISION AMPLIFIERS

UNDERSTAND SPICE-MODEL CONSTRUCTION TO APPRECIATE AC AND DC PERFORMANCE.

**BY DON LAFONTAINE • INTERSIL**

S

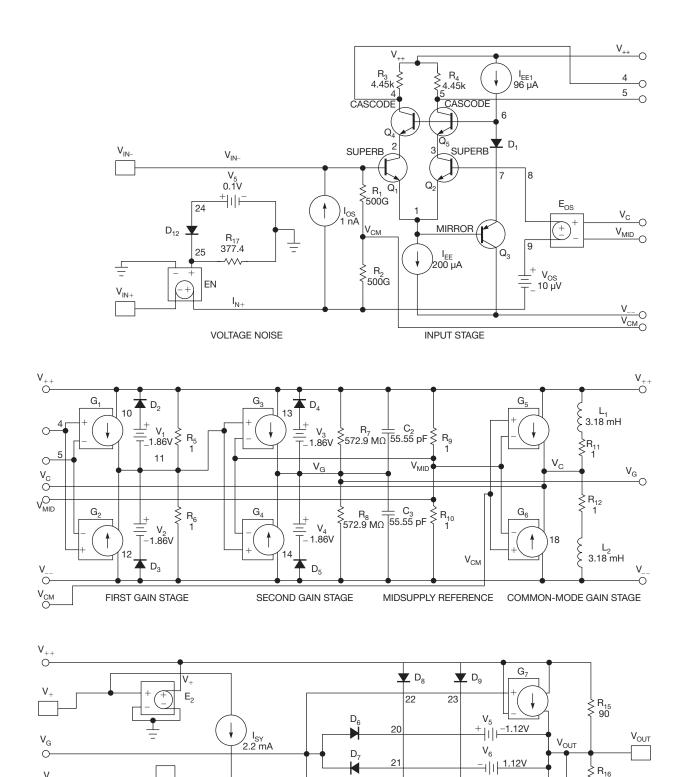

ystem engineers require accurate models for all types of ICs, and they require Spice models to run comprehensive circuit simulations. Early Spice models had few nonlinear elements, minimizing simulation time at the cost of accuracy, but new methods let you increase the number of nonlinear elements and improve accuracy. You

can create a multistage model for low-noise, low-power operational amplifiers. The model employs work from Analog Devices (**Reference 1**) and requires several architectural changes to model a low-noise, low-power precision amplifier. The model architecture processes the input signal through eight stages. You can easily calculate the parameters for the eight stages with a handheld calculator. To understand the model creation, you must have experience using Spice. Although higher-speed amplifiers have multiple poles and zeros, this model is for a single-pole, 10-MHz amplifier. It lets you simulate the amplifier's key ac and dc parameters. The model includes ac parameters for flicker and flatband noise, slew rate, CMRR (common-mode rejection ratio), gain, and phase. The model's dc parameters are  $V_{OS}$  (input offset voltage),  $I_{OS}$  (input offset current), quiescent supply current, and output-voltage swing. The model uses the 25°C typical parameters (**Reference 2**).

The closer you model the input stage to the actual amplifier, the more accurate your results will be. You can achieve an accurate ac representation of the amplifier's performance using a few of the process parameters of the input-stage transistors or MOSFETs. This model's architecture lets you model amplifiers with split supplies. There is no ground reference in any of the signal-processing blocks. After the differential-to-singleended conversion, all internally generated node voltages are referenced to the midpoint of the power supplies, much like the actual operation of an amplifier.

### **EIGHT CASCADED STAGES**

You build the model's circuit schematic with eight functional blocks (Figure 1). The only circuitry resembling an amplifier is the input stage (see Listing 1, which is available in the Web version of this article at www.edn. com/110303df). All other stages process the input signal with voltage-controlled current sources or voltage-controlled voltage sources. The stages might also include diodes, dc supplies, resistors, capacitors, and inductors.

The voltage-noise stage generates the flicker and flatband noise. To

#### AT A GLANCE

Model your op amps with detailed transistor-level input stages.

Set model parameters to replicate the low noise of your amplifier.

Properly characterize the supplycurrent usage to get an accurate model.

A procedure helps you set values in the eight stages of the model.

Correlate your simulations with real-world results.

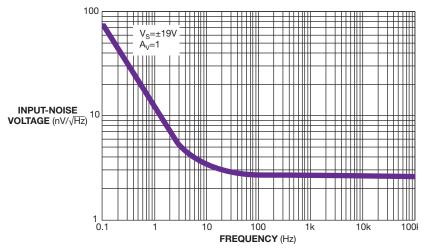

generate a flatband noise with only  $4 \text{ nV}/\sqrt{\text{Hz}}$ , set all diodes' and transistors' model parameters, kf and af, to zero and one, respectively. To lower the model's noise floor to single-digit nanovolts, it may be necessary to reduce the model's Johnson noise (**Reference 3**) by reducing the resistance values where possible.

Before reducing the resistor values, you calculate the standard resistor values and complete all the simulation tweaks. You then tweak the voltage-noise stage by reducing the resistor values to  $1\Omega$  and recalculating the transconductance and time constants of the stages to maintain the same transfer function. You can usually set resistors  $R_5$ ,  $R_6$ ,  $R_9$ ,  $R_{10}$ ,  $R_{11}$ , and  $R_{12}$  to 1 $\Omega$ . You need not reduce the Johnson noise if the amplifier you are modeling has hundreds of nanovolts of input noise. The initial noise simulations will tell you whether this step is necessary. Once you set the model's flatband noise below the amplifier's noise floor, you can change the flicker and flatband noise by adjusting  $D_N$ ,  $R_{17}$ , and  $V_5$ .

The input stage of the selected op amp comprises five bipolar transistors that model the actual IC configuration. For op amps with NMOS or PMOS stages, see **sidebar** "Typical input stages" in the Web version of this article at www.edn. com/110303df. The input stage includes a current supply to model  $I_{OS}$ , a voltage supply to model  $V_{OS}$ , and a voltage-controlled voltage source.  $R_1$  and  $R_2$  account for the CMRR of the device.

The first gain stage sets the combined

Probes Ringing RLGC Signal Integrity — Dr. Howard Johnson and his extraordinary Black Magic seminars... San Jose, CA **High-Speed Digital Design** 2-3 May 5-6 May Adv. High-Speed Signal Propagation 9-10 May **High-Speed Noise and Grounding Oxford University, UK** 21-22 June **High-Speed Digital Design** 23-24 June Adv. High-Speed Signal Propagation w.sigcon.com Use promo code: EDN11 For serious digital designers.

21

G<sub>10</sub>

**T** D<sub>11</sub>

G<sub>9</sub>

$\begin{cases} R_{16} \\ 90 \end{cases}$

$G_8$

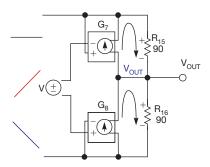

OUTPUT STAGE

4

**D**<sub>10</sub>

$E_3$

SUPPLY-ISOLATION STAGE

V\_

V

V\_ Ō gain of the input stage and the first gain stage to one, simplifying your calculation to determine the slew-rate-limiting components in the second gain stage. Diodes  $D_2$  through  $D_5$  and  $V_1$  through  $V_4$  clamp the output-voltage swing. Increasing the values of  $V_1$  through  $V_4$  will result in decreasing the maximum output-voltage swing. The maximum output-voltage swing,  $V_{OH}$ , is controlled by adjusting  $V_1$  and  $V_3$ , and the minimum output-voltage swing,  $V_{OL}$ , is controlled by  $V_2$  and  $V_4$ . Voltage limiting must take place in the open-loop gain stage; otherwise, succeeding nodes could attempt to simulate the generation of huge (hundreds of kilovolts) signals.

In the second gain stage, you set the open-loop voltage gain, bandwidth, and slew rate of the amplifier by adjusting transconductance blocks  $G_3$  and  $G_4$  and components  $R_7$ ,  $R_8$ ,  $C_2$ , and  $C_3$ .

The midsupply reference stage comprises two equal-value resistors,  $R_9$  and  $R_{10}$ . You use these resistors to generate a midsupply reference voltage. You set the resistor values to  $1\Omega$  to reduce the Johnson voltage noise of the model. The high current that flows through these resistors does not appear in the simulation results because of the supply-isolation stage.

The common-mode gain stage comprises two voltage-controlled current sources that drive two equal-value resistors in series with an inductor that connects to the supply rails (see sidebar "How the voltage-controlled-current-source stage works" in the Web version of this article at www.edn. com/110303df). The inductors simulate the fall-off of CMRR at higher input frequencies. You control the current sources with the input-common-mode voltage relative to the midsupply voltage. You generate the common-mode voltage with resistors  $R_1$  and  $R_2$  in the input stage. You set the transconductance of each source based on the reciprocal of the associated resistor value divided by the CMRR of the amplifier at dc. The inductors add a Z-plane zero to the common-mode gain, which is equivalent to adding a pole to the CMRR. After you scale and frequencyshape the common-mode voltage, you add it back into the input stage with a voltage-controlled voltage source, E<sub>os</sub>.

The supply-isolation stage comprises two voltage-controlled voltage sources and a current source. This stage enables you to program the total supply current of the amplifier with one entry in the node list. It also isolates the internal supply currents from the external supply current that the simulator sees, enabling the model to provide the correct quiescent supply current for low-power amplifiers with low voltage noise. The design trade-off is disabling the output-supply-current circuitry. By disabling this circuitry, the model does not account for the load current.

The output-stage operation is not obvious. After receiving appropriate frequency shaping, the amplifier's output signal appears as a voltage referenced to the midsupply at the inputs to  $G_7$  and  $G_8$ . Transconductance blocks  $G_7$  and  $G_8$  drive two equal-value resistors that connect to the supply rails. They act as active current generators. Both  $G_7$  and  $G_8$  generate just enough current to provide the desired voltage drop

| TABLE 1 OP-AMP SPECS     |                           |                                                    |  |  |  |  |

|--------------------------|---------------------------|----------------------------------------------------|--|--|--|--|

| Parameter                | Value                     | Comments                                           |  |  |  |  |

| Quiescent supply current | 0.0022A                   |                                                    |  |  |  |  |

| V <sub>cc</sub>          | 15V                       |                                                    |  |  |  |  |

| V <sub>EE</sub>          | –15V                      |                                                    |  |  |  |  |

| I <sub>EE</sub>          | 200 μA                    | Differential input-current source, or tail current |  |  |  |  |

| Slew rate                | 3.6×10 <sup>6</sup> V/sec |                                                    |  |  |  |  |

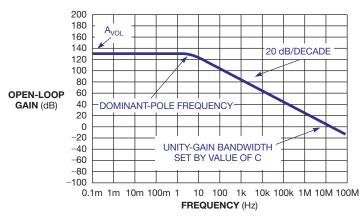

| F <sub>P1</sub>          | 5 Hz                      | Dominant pole from Figure 3                        |  |  |  |  |

| A <sub>VOL</sub>         | 264,000V/V                | 128.43 dB                                          |  |  |  |  |

| V <sub>os</sub>          | 1×10⁻⁵V                   |                                                    |  |  |  |  |

| I <sub>os</sub>          | 1×10 <sup>-9</sup> A      |                                                    |  |  |  |  |

| Temperature              | 25°C                      |                                                    |  |  |  |  |

| V <sub>T</sub>           | 0.0257V                   |                                                    |  |  |  |  |

| CMRR                     | 3.16×10 <sup>7</sup> V/V  | 150 dB                                             |  |  |  |  |

| F <sub>см</sub>          | 50 Hz                     | Common-mode pole                                   |  |  |  |  |

| R <sub>out</sub>         | 45Ω                       |                                                    |  |  |  |  |

| I <sub>sc</sub>          | 45 mA                     |                                                    |  |  |  |  |

| V <sub>oh</sub>          | 13.7V                     | Maximum output voltage                             |  |  |  |  |

| V <sub>ol</sub>          | -13.7V                    | Minimum output voltage                             |  |  |  |  |

across its parallel resistor (Figure 2).

HCO 28MS

Over 2500 Std.

Surface Mount

1-300 Watt Modules

**Programmable Models**

Military Upgrades Available

1509001-2000

AS 9100 REV B

for FREE PICO Catalog

in NY call 914-738-1400

Fax 914-738-8225

Electronics.Inc.

Call toll free 800-431-1064

143 Sparks Ave. Pelham, N.Y. 10803

E Mail: info@picoelectronics.com www.picoelectronics.com

Isolated/Regulated/

**Available**

Custom Models,

Consult Factory

-Stock to one we ample quantities

•From 2V to 10,000 VDC Output

**DC-DC Converters**

By simulating the right output resistance, you reduce the dc open-loop gain at the amplifier load. You model output short-circuit protection with diodes  $D_6$  and  $D_7$ , along with dc supplies  $V_5$  and  $V_6$ . Under fault conditions, the output voltage clamps to the previous frequency-shaping stage. You set the

Figure 2 A voltage-controlled voltage source's output stage has three modes of operation. When the input voltage is constant, the voltage drop across the resistors causes them to equally oppose each other. When the input voltage rises, the current in  $R_{16}$  increases, and the midpoint voltage increases. When the input voltage decreases, the current in  $R_{16}$  increases, the current in  $R_{16}$  increases, the current in  $R_{16}$  increases, the midpoint voltage decreases, the current in  $R_{16}$  increases, and the midpoint voltage decreases, the current in  $R_{16}$  decreases, and the midpoint voltage decreases, the current in  $R_{16}$  decreases, and the midpoint voltage decreases, the current in  $R_{16}$  decreases, and the midpoint voltage decreases.

output short-circuit-current limit by adjusting the values of  $V_5$  and  $V_6$ .

### **CALCULATE PARAMETERS**

To calculate the Spice model's parameters, you need various specifications from the op amp's data sheet and ICdesign information (Table 1). Putting the following equations into an Excel spreadsheet will enable you to change critical specs and quickly see the effect on the op amp's performance. You enter  $\mathrm{E}_{\mathrm{OS}}$  and  $\mathrm{I}_{\mathrm{OS}}$  from the data sheet directly into the model. You can often get the input-differential-capacitance spec, if your model requires it, from the data sheet. You determine the values of  $C_{2}$ and C<sub>3</sub> by relating the input differential-pair tail current,  $I_{EE}$ , to the amplifier's slew rate. This step establishes the maximum frequency for the single-pole RC network and sets the unity-gain bandwidth. Amplifier data sheets rarely state  $\boldsymbol{I}_{\text{EE}}$ , so you must get this value from the IC designer. For the amplifier of Reference 2, the equation works out to 55.55 pF:

$$C_2 = C_3 = \frac{I_{EE}}{\text{SLEW RATE}};$$

$C_2 = C_3 = \frac{200 \times 10^{-6}}{3.6 \times 10^6} = 55.55 \text{ pF}.$

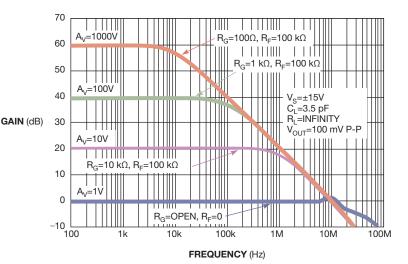

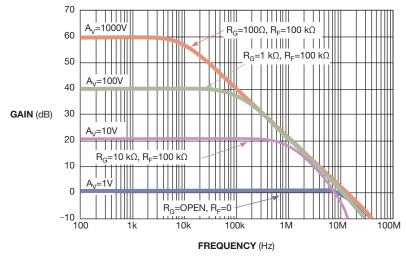

Figure 3 You use the  $A_{VOL}$ -versus-frequency chart in the IC's data sheet to determine the dominant-pole frequency.

You then determine the values of  $R_7$ and  $R_8$  by applying the dominant-pole frequency **equation**. This **equation** sets the breakpoint for the RC network. You observe  $f_{P1}$ , the dominant-pole frequency, by inspecting the open-loop gain chart in the amplifier's data sheet (**Figure 3**). The amplifier of **Reference** 2 yields a value of 573 M $\Omega$ :

$$R_7 = R_8 = \frac{1}{2\pi f_{Pl} C_{2/3}};$$

$$R_7 = R_8 = \frac{1}{2\pi (5)(55.55 \text{ pF})} = 572.958 \times 10^6.$$

You use the  $A_{VOL}$  from the data sheet and the resistance value  $R_{7/8}$  to determine the transconductance of the voltage-controlled current source:

$$G_{3}=G_{4}=\frac{A_{VOL}}{R_{7/8}};$$

$$G_{3}=G_{4}=\frac{2.64\times10^{6}}{572.958\times10^{6}}=4.6\times10^{-3}.$$

For the amplifier of **Reference 2**, the transconductance blocks solve to 0.0046. The model uses the first gain stage to set the combined gain of the input stage and the first gain stage to one. You can now calculate the voltage at the input of  $G_3$  and  $G_4$  to cause  $200 \times 10^{-6}$ , the tail current, to flow through  $R_7$  and  $R_8$ :

$$g_{m} = \frac{I}{V} \longrightarrow V_{G3/G4} = \frac{I}{g_{m}} = \frac{200 \times 10^{-6}}{4.6 \times 10^{-3}} = 43.4 \times 10^{-3}.$$

During slew-rate limit, the  $200 \times 10^{-6}$ current sink clamps the current through resistor R<sub>3</sub> or R<sub>4</sub>. With positive input voltage,  $R_4$  carries the current. Negative input means that the current will pass through R<sub>2</sub>. This current flows through the 4.45-k $\Omega$  resistor, resulting in a voltage drop of 0.89V. This voltage drop appears at the input to  $G_1$  and  $G_2$ . To set the combined gain of the input stage and the first stage to one, you must calculate the transconductance of  $G_1$  and  $G_2$  so that their output voltage equals 0.0434V when 0.89V is at their inputs. If you set the resistor value in parallel with the outputs of G<sub>1</sub> and  $G_2$  to  $1\Omega$ , the voltage will equal the current, and you can solve for the transconductance of  $G_1$  and  $G_2$ :

$$G_1 = G_2 \longrightarrow g_m = \frac{I}{V} =$$

$$\frac{43.4 \times 10^{-3}}{890 \times 10^{-3}} = 48.77 \times 10^{-3}.$$

If the design-review document is unavailable, set  $R_3$  and  $R_4$  to  $1\Omega$  for the calculation of the voltage appearing at the inputs to  $G_1$  and  $G_2$ . If you can get the collector currents from the IC designer, you can enter them directly into the model:

$$R_3 = R_4 = 4.45 \text{ k}\Omega.$$

You set  $V_{1/3}$  and  $V_{2/4}$  voltages for the maximum output-voltage swing:

$$\begin{split} &V_{1/3} = V_{\rm CC} - (V_{\rm OUTMAX}) + V_{\rm T} ln \, (\frac{2I_{\rm EE}}{I_{\rm S}}); \\ &V_{2/4} = (-V_{\rm OUTMAX}) - V_{\rm EE} + V_{\rm T} ln (\frac{2I_{\rm EE}}{I_{\rm S}}), \end{split}$$

### Introducing the easiest way to get your wireless product off the ground.

Enter the Anaren "BIG AIR" sweepstakes for your chance to win a snowboard gift card worth \$599!\* Go to www.bigairsweeps.com

snowboard

packages

Say hello to the industry's easiest, most elegant, and cost-effective RF implementation: AIR modules!

- Surface-mount module makes your product 'wireless' in record time – based on TI's CC1101 or CC2500 chips!

- Choose 433MHz, 800MHz, 900MHz, or 2.4GHz models – all with tiny, common footprints

- Virtually no RF engineering experience required

- FCC, Industry Canada/RSS, ETSI compliant (or pending) – no additional "Intentional Radiator" certifications required

To learn more, order samples, or obtain a quote – email AIR@anaren.com or contact one of these distributors.

\*NO PURCHASE NECESSARY TO ENTER OR WIN. PURCHASE OR PAYMENT OF ANY KIND WILL NOT INCREASE YOUR CHANCES OF WINNING. Sweepstakes will begin at 12:00 AM ET on January 1, 2011 and end at 11:59 PM ET ON MARCH 15, 2011. Open to all legal residents in the United States and Canada (excluding Quebec) that are 18 years of age or older as of 1/1/11 that are business owners or employees of businesses that design and/ or manufacture electronic products/equipment. THIS SWEEPSTAKES IS NOT OPEN TO THE GENREAL PUBLIC. For Official Rules, which include entry methods, prize description, and complete defails. Visit

www.bigairsweeps.com Sponsor: Anaren, Inc. Void where prohibited.

Texas Instruments

MCU Developer Networ

In Europe, call 44-2392-232392 ISO 9001 certified Visa/MasterCard accepted (except in Europe) where V<sub>T</sub>=0.02585V at T=25°C and I<sub>S</sub>=1×10<sup>-12</sup>A for both diodes. The model clamps the output voltage at a value equal to V<sub>CC</sub>+V<sub>D2/4</sub>-V<sub>1/3</sub> for positive input-voltage swings and  $-V_{EE}-V_{2/4}$ +V<sub>D3/5</sub> for negative input-voltage swings. For noise considerations, select a 1 $\Omega$  value for R<sub>11</sub> and R<sub>12</sub>:

$$R_{11} = R_{12} = 1\Omega$$

Calculate the values for  $G_7$  and  $G_8$ :

$$G_7 = G_8 = \frac{1}{R_{11/12} \times CMRR}$$

By inspecting the CMRR-over-frequency chart in the data sheet, you can estimate the common-mode pole frequency,  $f_{PCM}$ . This frequency lets you solve for the inductor values:

$$L_1 = L_2 = \frac{R_{11/12}}{2\pi f_{PCM}}$$

You set the output-stage transconductance equal to the reciprocal of  $2R_{OUT}$ :

$$G_7 = G_8 = G_9 = G_{10} = \frac{1}{2R_{OUT}}$$

This step results in unity gain through  $G_7$ ,  $G_8$ ,  $G_9$ , and  $G_{10}$ . You establish the output resistors as  $2R_{OUT}$  to account for the fact that the output current must appear to be coming from one supply rail:

$$R_{15}=R_{16}=2\times R_{OUT}$$

You can solve now for V<sub>5</sub>:

$$V_5 = I_{SC}R_{OUT} - V_{D6}$$

You create the absolute value of  $V_6$  by taking the absolute value of the first term:

$$V_6 = |I_{SC}R_{OUT}| - V_{D7}$$

#### SIMULATION RESULTS

Once you calculate all the model parameters, you can run the simulation. The simulations correlate well to the device's specified performance from the data sheet (**figures 4** through **9**). The IC's data sheet provides more comparisons of simulations to realworld results. Modern computing pow-

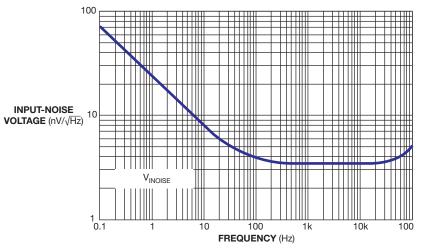

Figure 4 The measured input voltage noise spectral density has a flicker-noise corner and a 2.44 nV/ $\sqrt{\text{Hz}}$  flatband noise.

Figure 5 The simulated input voltage noise closely matches the flicker noise. The flatband noise is higher at 4 nV/ $\sqrt{Hz}$ .

Your Project Acceleration Resource for Electronics Manufacturing

### April 6–7, 2011 Boston Convention & Exhibition Center Boston, MA Electronics-NE.com

### **February 14–16, 2012** Anaheim Convention Center

Anaheim, CA ElectronicsWestShow.com

May 2–3, 2012 Charlotte Convention Center Charlotte, NC

Find the suppliers, tools, and services you need to make your product, process, and business more efficient, cost-effective, and profitable.

For information on attending or exhibiting, please call 310/445-4200 or visit CanonTradeShows.com

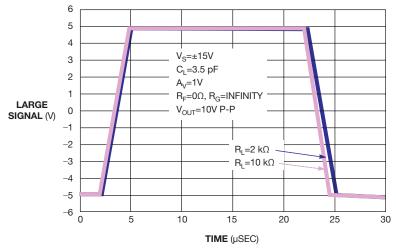

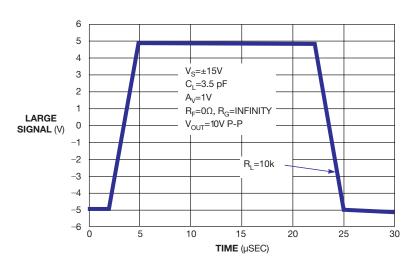

Figure 9 The simulated large-signal response is nearly identical to the measured results.

er quickly solves a model with five bipolar transistors in the input section. These transistors each have specific model parameters. Using this approach yields simulation results close to those of measurements of the part. In addi-

ALONG WITH THE ABILITY TO MODEL LOW SUPPLY CUR-RENTS, THIS PROCE-DURE IS IDEAL FOR MODERN LOW-NOISE, MICROPOWERED AMPLIFIERS.

tion, this procedure allows you to model single-digit nanovolt noise parameters. Along with the ability to model low supply currents, this procedure is ideal for modern low-noise, micropowered amplifiers.EDN

#### REFERENCES

Alexander, Mark, and Derek F Bowers, "SPICE-Compatible Op Amp Macro-Models," Application Note AN-138, Analog Devices, February 1990, http:// bit.ly/f1itjZ.

"Precision Single and Dual Low Noise Operational Amplifiers, ISL28127, ISL28227," Intersil Data Sheet, Dec 16, 2010, http://bit.ly/ i0tcDD.

Bowers, Derek F, "Minimizing Noise in Analog Bipolar Circuit Design," *IEEE Proceedings of the 1989 Bipolar Circuits and Technology Meeting*, Sept 18, 1989, pg 107, http://bit.ly/ ftdxMk.

#### **AUTHOR'S BIOGRAPHY**

Don LaFontaine is senior principal application engineer and senior engineering manager for Intersil's analog/mixed-signal product line

(Palm Bay, FL), where he has worked for 30 years, focusing on precision analog products. He has a bachelor's degree in electrical engineering from the University of South Florida (Tampa, FL). His personal interests include family, surfing, and dirt-biking. You can reach him at dlafonta@intersil.com.

New England's Project Acceleration Resource for Electronics Manufacturing

April 6-7, 2011 Boston Convention & Exhibition Center Boston. MA

Your face-to-face meeting place for the latest technologies in electronics manufacturing, including:

- Electronic Manufacturing Services

- Testing & Inspection Equipment

- Automated Assembly Machines & Systems

- Board Level Components

- Computers/Peripherals/Software

- PCB Productions Equipment

- Embedded Devices

- ... and much more

Supported by:

Register Today at: Electronics-NE.com Please use Promo Code AA

Produced and Managed by UBM Canon, 11444 W. Olympic Blvd., Los Angeles, CA, 90064-1549 Tel: 310/445-4200 ubmcanon.com

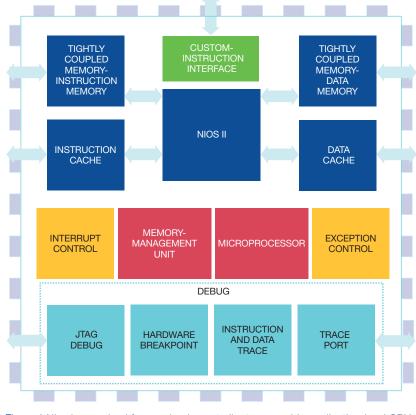

### CPUS IN FPGAS: MANY FACES TO WHETHER AS SYNTHESIZABLE SOFT CORES OR HARD CORES ON THE DIE, CPUS ARE SHOWING UP IN MORE FPGA DESIGNS, BRINGING WITH THEM IMPORTANT CHALLENGES FOR DESIGNERS.

PU cores in FPGAs have a history reaching back to the early years of the FPGA's existence and a future extending far into the realms of microcontrollers and ASSPs (application-specific standard products). We are now at an inflection point in that trajectory, facing manifold options. CPU cores may be soft—synthe-

sizable cores that go into the FPGA's programmable logic—or hard—cell-based blocks that the FPGA vendor builds directly onto the die. The CPU architecture may be industry-standard, proprietary to the FPGA vendor, or unique. Processing capability spans tiny 8-bit microcontroller cores and 32-bit CPU clusters with DSP extensions. All this diversity conceals profound differences in implementation flow, in system performance, and in debugging access, all of which demand exploration. more ports, allowing different pipeline stages to initiate address calculations, do scalar arithmetic, and save results, all in the same cycle. The only options for implementing general registers in an FPGA, however, are the inherently single-port LUTs (look-up tables) in the logic cells or the block RAMs. Either option requires a wrapper of logic cells to emulate large-scale multiport access. The result, once you synthesize it into an FPGA, may be functionally correct, but either it significantly lowers the CPU's maximum frequency or the designer must significantly reorganize the execution pipeline.

Critical paths in general present problems for the FPGA adaptation of

# South Strate State and State and State and State and State and State

#### **EXPLAINING DIFFERENCES**

To understand the current nature of CPUs in FPGAs, it helps to have a little perspective. Early FPGAs, confined by their limited capacity, lived beside a microprocessor or a microcontroller, implementing glue logic or, more grandly, a bus bridge. With Moore's Law and human nature on the march, however, FPGAs grew. Users began to dream of implementing their own CPU designs—every digital designers' Holy Grail—in FPGAs.

Early attempts had modest goals: 4-bit microcontrollers, for example. Even in these low-gate-count undertakings, however, designers began to discover issues about implementing a CPU core in programmable fabric.

Some issues are structural. Implementers of discrete CPU cores have available a mixture of standard-cell and full-custom techniques. These riches allow architects to use structures that give them the best performance for the power and area, knowing that the implementation team has the tools to do its part of the job. Those structures may not make any sense in an FPGA fabric, however. For instance, FPGAs and shared tristate buses do not get along well together. Another example would be the fast-often single-cycle-multiport register files at the heart of CPU design. In advanced architectures, the general-register files may have eight or

a CPU. A designer of silicon cores can simply minimize the number of negative-slack paths and then throw at them a whole battery of tricks: low-threshold cells, high-drive cells, custom cells, and hand placement and routing. None of these techniques is readily available to the typical FPGA user.

As FPGA users began to lust after more substantial cores, such as the elegant ColdFire or the ubiquitous ARM7, implementation realities limited the attractiveness of the whole idea. Many designers began to believe that CPU cores in FPGAs were big, slow, power-hungry, and generally not worth the trouble.

Engineers don't stay frustrated for long, though. About 10 years ago, de-